地址:

北京市朝阳区广顺北大街33号院1号楼1单元6685号

工作时间

周一至周五: 9AM - 7PM

周末: 10AM - 5PM

地址:

北京市朝阳区广顺北大街33号院1号楼1单元6685号

工作时间

周一至周五: 9AM - 7PM

周末: 10AM - 5PM

⚡️ 深入纳秒世界,揭秘HFT架构的终极形态

高频交易(High-Frequency Trading, HFT)系统是金融与工程技术的巅峰结合,其架构旨在以微秒乃至纳秒级的速度完成交易决策和执行。下面将从整体架构、关键组件及核心技术、其他要点和未来展望四个方面,对HFT系统的设计进行深入介绍。

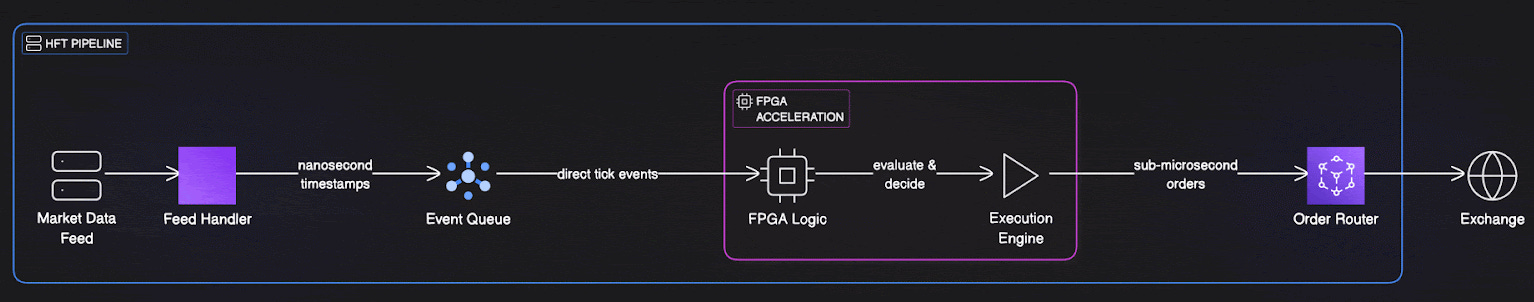

HFT系统的整体架构可以视作一个端到端的“闪电”交易流水线,从市场数据获取到交易执行,力求极致缩短每个环节的延迟。典型流程包括:行情数据获取(连接交易所直连行情源)、实时数据处理(解析行情并更新内存订单簿)、策略决策(算法根据最新行情瞬时做出下单决策)、订单路由与执行(通过智能路由发送订单到最佳交易场所执行)、风险管理(全程监控交易风险并施加风控)等模块。这些模块彼此紧密衔接,形成微秒级触发的事件驱动流水线,实现“行情触发决策,决策产生订单”的闭环。

图1:高频交易系统简化流水线示意图。从市场行情输入,到Feed Handler解析进入事件队列,策略引擎(软件或FPGA加速)对事件做出决策,经订单路由发送到交易所。整个流程经过高度优化,追求微秒级的tick-to-trade延迟。

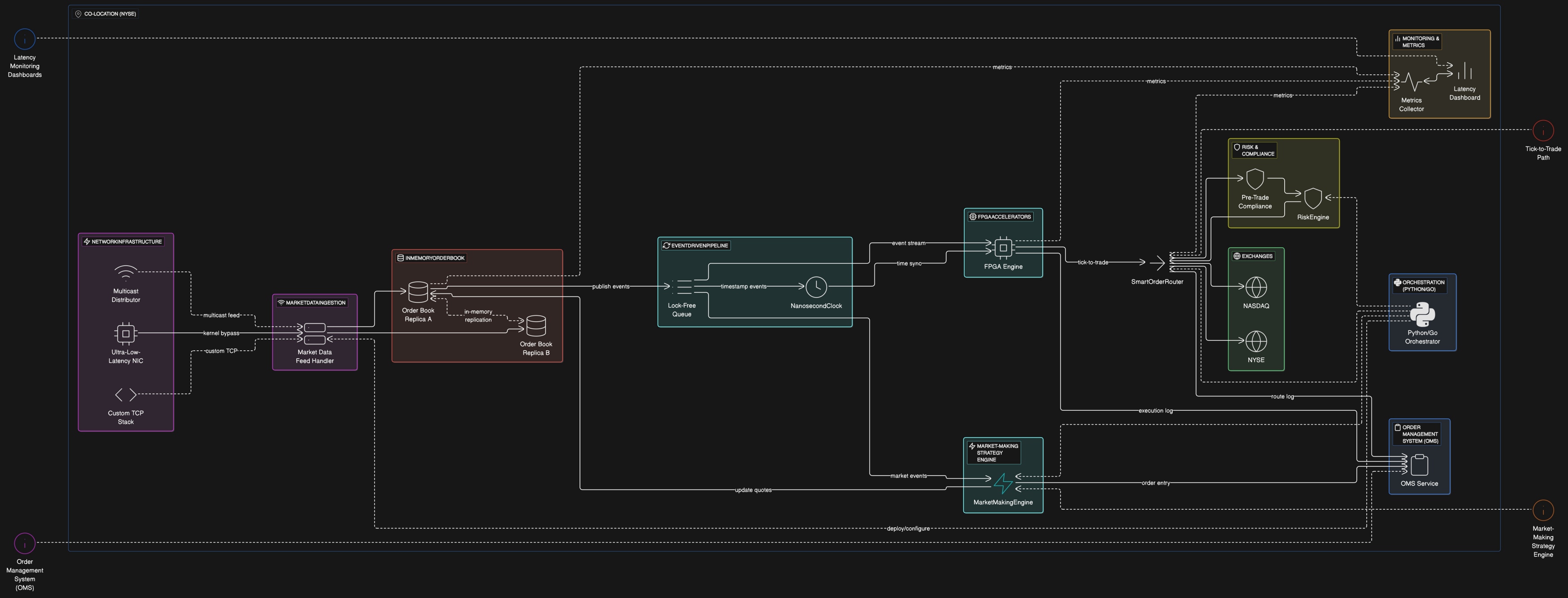

在这种架构下,市场数据通过超低延迟网络接口被捕获后,直接送入专门的行情处理模块;处理后的订单簿快照触发策略引擎做出交易决定;订单管理与路由模块将交易指令发往交易所撮合执行,同时风险控制模块实时校验交易指令是否合法、安全。整个系统通常部署在交易所附近的同地机房,以物理距离最小化通信延迟,并采用纳秒级精度时钟对各环节打点监控,以衡量端到端延迟及各阶段耗时。可以说,每一微秒的延迟都被视为至关重要,贯穿架构设计的各个角落。

图2:某高频交易系统完整架构示意图。涵盖从市场数据采集、内存订单簿、策略引擎(含部分FPGA逻辑)、到订单管理路由、风险控制的全流程。各组件均部署了精密监控(如纳秒时间戳记录)和冗余容错机制,实现微秒级性能和高可用。

高频交易系统由一系列高度特化的组件构成,每个组件都采用了先进的技术来追求极致性能。下面我们按模块对关键组件及核心技术进行介绍。

市场数据采集是HFT系统的起点。HFT系统直接接入交易所的行情数据源,以获取毫微秒级的市场状态更新。为了尽量减少延迟,HFT系统使用超低延迟网络接口卡(NIC),并启用内核旁路(Kernel Bypass)等技术使数据包直接在用户态处理,跳过操作系统网络栈带来的开销。

行情数据抵达后由行情Feed处理器进行解析,它需要实时解码每秒成百上千万条市场消息。解析的正确性和效率至关重要——任何一次解析错误都可能导致交易算法做出错误决策,造成巨大损失。因此行情处理模块通常采用高度优化的解析逻辑和数据结构,尽可能利用并行处理,同时确保解析过程的确定性和稳定低延迟。

内存订单簿(In-Memory Order Book)是HFT系统的大脑,用于维护市场上每支交易品种的当前买卖报单状态。由于行情更新频率极高,传统数据库或基于磁盘的存储难以支撑微秒级的更新要求,因此HFT系统将完整订单簿保存在内存中,通过特制的数据结构实现快速更新和查询。每当有新的买单或卖单报价进来,系统会立即更新内存订单簿,重新计算最新的买一/卖一价格、市场深度等派生信息,以供策略决策参考。维护内存订单簿面临严峻的性能挑战。一些活跃股票每秒可能有数以千计的订单更新,每一条更新都必须严格按时间顺序处理,更新相关聚合统计(如成交量加权均价、流动性不均衡指标等)。系统必须小心避免任何锁竞争或线程同步问题,因为哪怕微秒级的延迟都可能让竞争对手占得先机。为此,HFT系统通常采用无锁或细粒度锁的数据结构,以及多副本冗余机制:维护同一订单簿的多个同步副本分布在不同CPU核心甚至不同服务器上。如果某个副本由于垃圾回收或意外错误滞后,系统可以瞬时切换到另一副本,保证订单簿更新不中断。这种多副本架构提高了系统的容错性与故障转移能力。

策略引擎(交易算法模块)是HFT系统的决策中心。这里运行着各种量化交易策略,从简单的做市策略到复杂的跨市场套利、机器学习模型。HFT策略的共同特点是追求极低的决策延迟和确定性的执行。算法需要在微秒内对市场变动做出反应,捕捉稍纵即逝的套利机会。例如知名的延迟套利策略中,当检测到某股票在交易所A的报价变动尚未传播到稍慢的交易所B时,HFT系统会抢先在B交易所下单,利用这几个微秒的信息不对称获取无风险利润。

为了在极短时间内完成复杂计算,策略引擎大量采用性能优化手段。例如,尽量避免在热路径上执行浮点计算或复杂函数,而是预先计算并存储查找表用于快速查值,以空间换时间。很多HFT算法会预先离线推演成千上万种情景,把可能的决策结果存成哈希表或数组,在实盘中根据当前行情状态直接查表得到决策。此外,策略代码要求完全确定性,避免由于线程调度、竞态条件导致的不一致。针对此,常用技术包括使用单线程或锁凝缩的事件驱动模型,或借助FPGA等硬件来保证确定性。

值得一提的是,一些HFT公司已经开始探索将机器学习模型融入策略引擎,用于预测短期价格走势或交易对手行为。但复杂模型往往意味着更高的计算量,如何在不牺牲延迟的前提下利用机器学习,是一个前沿挑战。目前业界普遍做法是离线训练、在线简化:离线用海量历史数据训练模型,在线交易时使用简化版本模型或将模型输出预先计算为查找表,以确保实时决策依然足够快。

HFT系统对网络延迟的苛刻要求促使它们在网络通信层面做出特殊优化。首先是将交易服务器物理部署在交易所数据中心内或附近,实现同地托管(Co-location),以减少物理距离造成的信号传输延迟。其次,在网络栈上广泛应用内核旁路技术,使应用程序直接与网络硬件交互。典型实现包括:DPDK(数据面开发套件)使用户态程序以轮询方式直接收发网卡数据包、RDMA(远程直接内存访问)在机器间直接传输内存数据、PF_RING ZC零拷贝包处理、OpenOnload用户态协议栈绕过内核等。通过这些技术,网络报文从网卡到应用的路径被极大缩短,可以将网络收发延迟压缩到微秒级别甚至亚微秒级别。

此外,HFT系统偏好使用UDP协议等简化网络传输,并定制网络交换设备(如低延迟交换机,甚至使用微波通信或激光链路替代部分光纤传输)来进一步缩短跨地域传输时间。当行情从交易所发出到HFT服务器接收并做出响应,这中间每一步网络跳转都经过精心优化,以争取哪怕几纳秒的优势。

当软件优化达到极限时,HFT系统会求助于FPGA等专用硬件加速器。现场可编程门阵列(FPGA)能够将交易逻辑直接烧录在硬件电路中运行,避免了指令流水线、操作系统中断等软件开销。在FPGA上,市场数据的处理和策略决策以纯硬件电路的方式并行执行,其响应速度之快令人瞠目——被称为Tick-to-Trade延迟,即从收到行情Tick到发出交易指令所需的时间。纯软件系统通常Tick-to-Trade约为10~50微秒,而FPGA方案可以缩短到不到1微秒。这意味着FPGA能够在竞争对手的软件系统尚未反应过来之前,抢先完成下单。

使用FPGA的代价是开发复杂度和灵活性。硬件逻辑开发需要使用硬件描述语言(如Verilog/VHDL)设计电路,更新策略需要重新综合电路并烧录FPGA,往往耗费数小时且无法频繁迭代。因此许多HFT公司采取软硬结合的架构:将最关键、对延迟要求极致的部分策略部署在FPGA中,其余逻辑仍由软件实现。这样既能发挥FPGA速度优势,又保留了一定的灵活性,可以通过软件快速更新策略。在软硬件协同的架构下,FPGA往往承担最核心的行情触发交易逻辑,而风险控制、复杂策略计算等更高级别功能交由软件模块处理。

HFT系统虽然以速度制胜,但风险控制绝不能被速度牺牲。在微秒之间做出交易决策的同时,系统必须实时评估风险并执行风控措施,以防止失控的算法造成巨大损失。历史上曾发生过著名的Knight Capital事件:算法失灵在45分钟内亏损4.4亿美元,就是由于缺乏有效的实时风控拦截。

为避免此类灾难,HFT系统会在每次下单前通过交易前风险检查(Pre-Trade Risk Checks)来验证订单的合理性。这些检查包括:持仓和敞口限制(确保某股票净持仓不超上限)、单笔订单规模限制、价格偏离检查、交易频率限制,以及合规检查等。一旦发现订单可能违反风险控制规则,系统会立即阻止下单,或在极端情况下触发“杀死开关”(Kill Switch)暂停整个策略。由于HFT系统无法容忍哪怕毫秒级的风控延迟,这些风险检查一般也在内存中完成,使用预先计算好的阈值和风控模型以换取速度。例如,系统在内存维护实时更新的持仓和PnL状态,这样检查单笔新订单对持仓是否超限时,只需 O(1) 时间读取当前持仓并比较即可。部分领先的HFT架构甚至将风险控制逻辑下沉到FPGA或者网卡Firmware层,实现纳秒级别的风险监测。

除了交易前检查,HFT风险管理系统还持续进行事中和事后监控。例如持续监测账户资金和保证金情况、交易指令是否异常(如短时间内大量重复报撤单可能暗示系统故障)、策略盈亏曲线等。一套完善的风控系统如同高频交易的安全网,在保证不显著增加延迟的前提下,尽最大可能降低意外损失和合规风险。

订单管理系统(OMS)是负责生成、跟踪和管理交易指令的模块。在HFT环境中,OMS需要高效处理海量订单的创建与状态更新,并与交易所保持高速通信。为此,OMS通常采取内存数据库或高速缓存来存储活动订单信息,并行处理多个订单事件,以及采用优化的数据结构(如哈希表索引订单)以实现毫秒以下的订单查询与更新。当策略引擎发出交易信号,OMS会生成订单并调用执行引擎连接交易所网关完成下单。在多市场交易的场景下,OMS通常结合智能订单路由(SOR)功能:即根据订单的属性和各交易所实时流动性,智能地决定将订单发送到哪个市场、使用何种订单类型,以及是否拆分到多个场所以获得最优执行效果。例如,当策略决定买入1000股某股票时,系统可能需要评估NYSE和NASDAQ等多个交易所的订单簿情况,选择流动性更好的市场,或者将订单拆分成多笔小单分别在不同交易所同时下单,以减少冲击成本和交易滑点。这一过程需要考虑当前流动性、历史成交概率、交易费用、潜在的信息泄露风险等众多因素,而且必须在微秒内完成计算。

执行层面,为了统一不同交易所的接口,HFT系统广泛使用FIX协议或交易所提供的原生API,实现低延迟的报单通信。执行引擎组件负责维护与各交易所的会话连接,监控订单的回报(如确认、成交、撤单回报),并将状态更新反馈给OMS记录。高性能HFT系统往往能并行管理成千上万笔活跃订单,同时每秒处理上万条订单状态更新而不掉队。

除了核心交易流水线,高频交易系统在性能监控、高可用架构以及测试仿真等方面也有特殊的设计考量,以保障系统稳定运行并持续优化。

HFT系统对性能监控和延迟分析的要求极高,因为任何微小的性能劣化都会直接影响收益。为此,这些系统内部植入了精细的测量和监控机制。例如,在行情从输入到订单发出的整个流程中,HFT系统使用纳秒精度的时钟对每个事件进行时间戳标记,以统计每个阶段的耗时。运维团队可以通过这些数据计算出端到端延迟的均值、99百分位尾部延迟,以及检测是否存在异常的抖动(jitter)。实时监控仪表盘会展示系统各组件的运行健康状况、当前每秒处理的消息数、策略盈亏等信息。一旦某环节延迟异常升高或出现错误,系统能够立即报警,必要时自动切换到备用系统以避免交易中断。

监控还包括对交易性能指标的跟踪。例如订单的成交率、拒单率、每秒交易数量、持仓风险度等都是关键指标。这些数据帮助工程师发现潜在瓶颈(比如某策略决策耗时开始逼近阈值)并进行针对性优化。HFT公司甚至会对部署在不同地域的数据中心之间的时钟进行校准同步(如使用PTP精密授时协议),以准确衡量跨地域套利交易的延迟。

高可用性对高频交易系统至关重要,因为哪怕几秒钟的停机都可能导致重大的交易机会损失或风险暴露。HFT系统通过多层冗余来实现几近实时的故障转移。正如前文提到的内存订单簿会有多副本冗余,同样在整个系统层面,也会部署热备容灾架构:关键服务器成对部署,主用机器发生故障时,备用机器能在微秒级内接管交易。这种快速故障切换通常通过心跳监测和硬件级的切换来实现。例如两台共定位服务器同时接收行情和维护订单簿,当主服务器异常停止响应数毫秒内,备机已实时同步状态并无缝承担交易流。

在网络连接上,HFT系统也会准备冗余链路,防止单点故障。包括多条独立的物理光纤路径、冗余交换机和路由设备等。软件层面,通过进程守护和自动重启机制,确保任何模块异常退出都能立刻重启恢复。许多交易公司还构建了多地部署的灾备系统,以应对本地数据中心断电等极端事故。虽然跨地域切换会增加一定延迟,但至少保证在无法交易所所在地部署时还能继续交易或平仓,降低风险。

总的来说,高频交易架构把“不间断运行”作为首要目标之一,系统设计时就考虑各种故障场景的应对,如同F1赛车配有备用引擎和轮胎,HFT系统也准备了周全的备份和最快的修复策略。

构建HFT系统还需要重视测试和仿真,因为在真实市场中试错代价极高。开发团队通常搭建完善的模拟交易环境,重放历史行情或生成模拟行情,让策略在不影响真实市场的情况下验证表现。这种仿真系统必须能够以加速模式重演历史高频数据,例如用1小时的时间重播1天的行情,以测试策略在高负荷下的稳定性和反应速度。

回测(Backtesting)是策略开发的重要环节,它使用历史数据评估策略在过去的表现。HFT系统的回测需要精细地模拟真实交易的时序和延迟,比如考虑到撮合延迟、网络延迟,否则回测结果可能不可靠。先进的HFT团队把回测和仿真集成到日常的CI/CD流水线中——每当策略代码更新,就自动在历史数据上跑仿真测试,验证收益曲线和风险指标是否有显著变化。一些风险控制措施(例如新的风控参数)在部署前也会通过仿真环境进行“压力测试”,确保不会误杀正常交易或漏拦截风险。通过持续测试,HFT系统在飞速迭代策略的同时,尽量避免出现重大纰漏,保障上线版本的稳健性。

除了离线仿真,有的HFT平台还支持“影子交易”机制:即在真实市场实时运行策略的同时,影子账户用同样的行情输入并策略逻辑跟单生成模拟订单,不实际下单,以检验新策略或新代码在实盘环境下的表现。这种在线仿真进一步降低了策略发布的风险。

高频交易系统的架构设计围绕着极致性能和可靠性展开,可总结出以下设计原则和挑战:

总而言之,高频交易系统的架构是一门追求极致优化的艺术。在这个领域,工程师不但需要考虑算法和数据结构,还要综合考虑物理定律与硬件极限,把时间本身作为竞逐的对象。未来的高频交易将继续推动技术边界,一如既往地在纳秒之间寻找利润。在这场军备竞赛中,胜者将是那些既掌握前沿技术又严守风险管理的人。高频交易系统的演进,也将不断为更广泛的实时计算领域带来启示和创新。